Silicon carbide (SiC) substrate-based chips are on the (very) fast track due to SiC challenges. The automotive industry wants SiC chips so it can increase electric vehicle (EV) range and decrease charging time. The telecom industry wants them for 6G. And the renewable energy folks want them for more efficient power generation and storage.

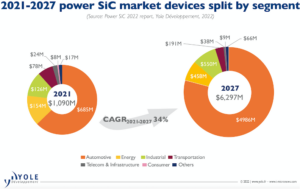

(Courtesy: Yole Développement)

The latest figures from Yole Développement indicate the power SiC market is growing at a rate of 34%, so it should break through the $6 billion mark in the next five years. Meanwhile, gallium nitride (GaN) on silicon carbide, which is used primarily in the telecom and defense industries, is growing at a very respectable 17% CAGR, says Yole.

Indeed, SiC solves many problems, especially related to heat, voltage and frequency. But it also creates a lot of headaches for wafer and chip manufacturers. SiC wafers are very expensive, time consuming and energy-intensive to produce. Additionally, manufacturing devices on SiC wafers require specially adapted equipment and processes. In both cases, yield is an enormous SiC challenge.

It starts with the wafers

First comes the wafer manufacturing challenge. Silicon wafers are cheap. The low price tag starts with the ingots from which they’re sliced, which are grown in a matter of hours. Wafering (the slicing process) is also fast and produces hundreds of wafers per ingot.

Then consider the 12 or so steps for producing SiC wafers. They start with growing the boules, which look more like hockey pucks than ingots, and take weeks to grow in ovens almost half as hot as the sun. Each wafer is then painstakingly sawed off the boule with a diamond saw. If you’re lucky, you get 40, maybe 60 wafers off a boule, but yield is often very low.

The resulting SiC wafers are half as thick as silicon, very brittle, and require substantial processing to meet the draconian requirements of device manufacturers. Plus, they’re transparent, so the traditional sensors used in handling can’t even see them properly. Equipment manufacturers have incorporated new generations of sensors into their tools just so they can identify and lift the SiC wafers without breaking them. And of course, being so fragile, these wafers tend to bow, and require special materials, processes and handling equipment for post-wafering cleaning and polishing.

On to devices

Then you’ve got these transparent, brittle and expensive SiC wafers to nurse through the device manufacturing process. (By the way, this is true for both straight SiC wafers and GaN-on-SiC wafers.)

Start by considering challenges of ion implantation. Dopants will not diffuse into the SiC like they do into silicon: They want to form craters. The requisite anneal at 1800oC can carbonize the surface.

Next consider the steps related to lithography. The tendency of these ultra-thin SiC wafers to bow challenges the photo process. A thick layer of photoresist must be spun onto the wafer and patterned before the metal deposition. The tools need to be able to handle the bowing.

Metal deposition? Another challenge. The thick layers of metals such as gold, nickel, copper and silver/tin must be deposited with excellent uniformity without damaging the brittle wafer.

Once the metals have been deposited, the photoresist must be removed. Easy? Of course not. The standard sulfuric peroxide mix (SPM) processes will attack the metal. Instead, the wafers with their thick photoresist are soaked in a tank of solvents for a set amount of time, then transferred to a single wafer chamber for a final clean and dry.

Etch? Think again. Some of the metals cannot be etched using a specific chemistry, so the patterning of the metal is done using a sacrificial layer of photoresist. That layer is patterned using traditional methods, then the metal is deposited on top. The final step is to dissolve the resist, lifting away any metal on top and leaving the rest of the patterned metal.

At the cleaning forefront

As a leading supplier of cleaning tools for both SiC wafer and device manufacturing, ACM has had a front-row seat to the challenges. We’ve worked closely with our customers to address those challenges, adapting our equipment to the specificities of SiC wafer and device manufacturing. All our SiC-enabled tools are equipped with state-of-the-art sensors so the wafers can be identified and carefully handled.

In tools for wafer manufacturing, we’ve also equipped our post-CMP tool with doubled-sided brushing and a clean step. This removes all the slurry and SiC residues after wafer polishing.

Our tools used for cleaning during the various device manufacturing steps are also equipped with handling systems that can cope with the bow and transparency of SiC wafers. They include:

- The ACM Ultra C coater and Ultra C developer handles all the exigencies of photoresist coating and development

- The ACM Ultra C GIII deposits the thick metal layers with excellent uniformity without damaging the brittle wafers

- The ACM Ultra C PR stripper has been adapted into a combined soak and single-wafer tool to remove the thick photoresist once the metals have been deposited

- The ACM Smart Megasonix™ system enables the resist removal, lifting away any metal on top while leaving the rest of the patterned metal. For SiC, the system has been further adapted to a single wafer chamber with the appropriate solvent, which can be filtered and recycled. A final rinse with deionized water (DIW) is followed by a drying step.

- The ACM Ultra C SAPS II/V tool has been equipped with a choice of binary nozzle or ACM’s proprietary Smart Megasonix™ for cleaning with dHF, SC1 and SC2

As the demand for SiC-based chips continues its upward trajectory, increasing throughput will become even more important. At ACM Research, we are rising to the challenge. We also have new equipment forthcoming that is specially dedicated to SiC wafer cleaning. Be on the lookout!